如何测量IO的VIL和VIH?

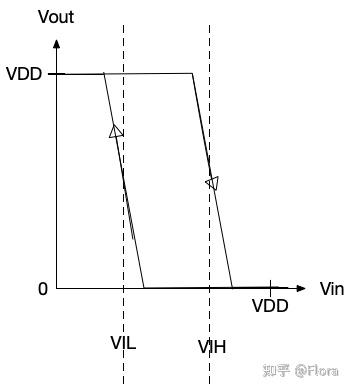

IO端口作为输入端口时,一般内嵌迟滞(hysteresis),以抵抗噪声干扰。以反相器结构为例,输入要高于某电平(VIH)时,输出才翻转为0,反之输入要低于某电平(VIL)时,输出才翻转为VDD。有关系式VDD>VIH>0.5*VDD>VIL>0. 示意图如下:

按正常逻辑,输入给逐步给一个DC电压值,就可以测得VIH/VIL. 事实上,依据的原理也确实是如此。但如果直接用电压源接入CMOS反相器结构电路(也就是常成为SMIT trigger)的输入端,会存在一些问题。测量时输入在VIL和VIH之间时,输出结果在0和VDD之间跳变。分析出的原因是CMOS反相器输入为高阻抗,当其直接与理想电源相接时,很容易受噪声干扰,导致输入端口电压波动大。当这个电压波动范围大于hysteresis window时,就会观察到输入在中间电平附近时输出在0和VDD之间跳变。

解决办法。一是在输入端,挂上电容(uF级别),起滤波作用,使得测量的输入信号是单调地上升或者单调地下降。二是在输入端并上电阻,从电源看到的输入端为低阻点,其电压不易受噪声的影响,因此输入端电压在中间电平附近时,输出依据前一个输出状态给出确定的输出电平。但是该方法还是不能改善过冲带来的影响,导致测出来的hysteresis window可能比实际测量得到的结果小。

编辑于 2021-07-21 00:26